Xentium DSP Radiation-hardened IP core

Tijdens wetenschappelijke missies in de ruimte verzamelen moderne instrumenten en sensoren zo veel data dat deze niet in zijn geheel naar de aarde kan worden gecommuniceerd. Daarom moet de data ter plekke, in de ruimte worden geanalyseerd en gecomprimeerd voordat deze naar de aarde wordt gezonden. De digitale componenten die deze taken uitvoeren moeten bestand zijn tegen de schadelijke invloed van kosmische straling. Alleen stralingsbestendige apparatuur is geschikt voor ruimtemissies. Onze Xentium Digital Signal Processor IP-core is ontworpen met de barre omstandigheden van de ruimte in gedachten. Deze extreem betrouwbare, fouttolerante IP-core voor digitale signaalverwerking doet zijn werk ook in de moeilijkste omstandigheden.

Onze stralingsharde IP-cores:

Stralingsbestendige dataprocessor-IP

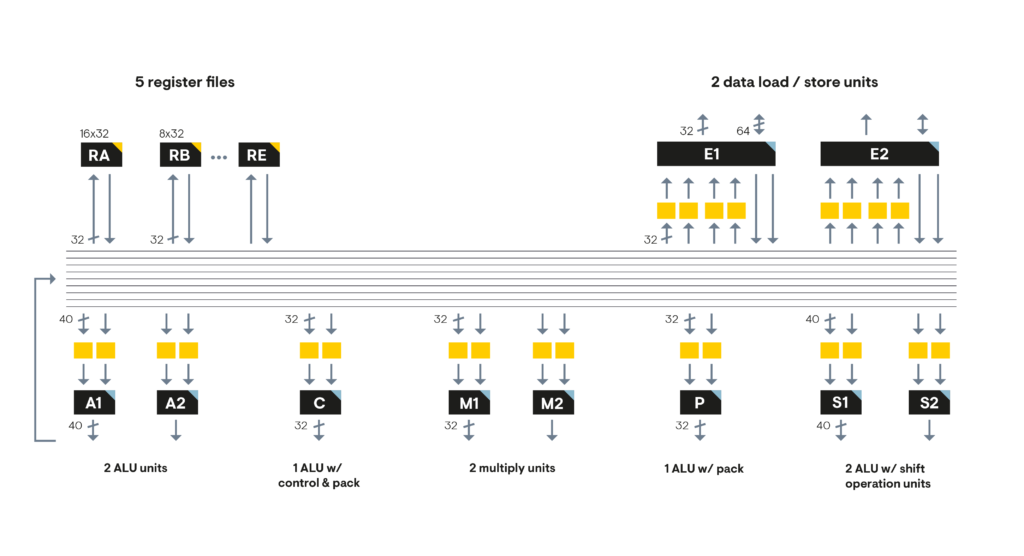

De Xentium is een VLIW (Very Long Instruction Word) DSP-core met hoge prestaties en een laag energieverbruik. Het grootste voordeel van deze VLIW-core is dat de complexiteit wordt verschoven van de elektronica naar de compiler, waardoor de elektronica kleiner en energie-zuiniger kan worden. De Xentium ondersteunt zowel 32-bits fixed-point bewerkingen als enkelvoudige precisie FMA-bewerkingen (fused multiply-add). Het is een zeer schaalbaar IP-bouwblok dat geschikt is voor grote multi-core SoC’s (System-on-Chip). De Xentium kan ook worden ingezet als DSP-versneller in combinatie met een processor voor algemene doeleinden, zoals de FreNox RISC-V.

De Xentium combineert grote rekenkracht met een laag energieverbruik en een kleine silicium voetafdruk. Met geavanceerde besturingsmechanismes worden inactieve componenten uitgeschakeld tijdens de uitvoering van DSP-loops. Hierdoor wordt de omvang van de code beperkt en de energiezuinigheid vergroot. Een strak gekoppeld datageheugen zorgt voor een nog lager energieverbruik en een efficiëntere verwerking. De Xentium DSP IP-core wordt geleverd met een software-ontwikkelomgeving op basis van C, inclusief een toolchain die bestaat uit een C-compiler met een standaard C-library, een assembler, een linker, een simulator, een debugger en een aantal andere hulpprogramma’s.

Ontwikkeld met ruimtevaartorganisatie ESA

De Xentium DSP IP core is ontwikkeld in nauwe samenwerking met de Europese Ruimtevaartorganisatie ESA. Voor het Cosmic Vision programma had ESA een standaard ASIC nodig met een stralingsbestendige digitale signaalprocessor die geschikt was voor gebruik in de ruimte en die een snelheid had van minimaal 1 GFLOP’s (één miljard floating-point bewerkingen per seconde). Voorafgaand aan de implementatie van de multi-core DSP SoC-architectuur in stralingsbestendige siliciumtechnologie werd de functionaliteit gevalideerd met een prototype op basis van commerciële FPGA-technologie. Het ontwikkelproject had meerdere fases en resulteerde in een betrouwbare, fouttolerante, stralingsbestendige DSP-IP voor de verwerking van sensordata in de ruimte met optimale processorkracht.

FPGA met multi-core Xentium SoC architectuur

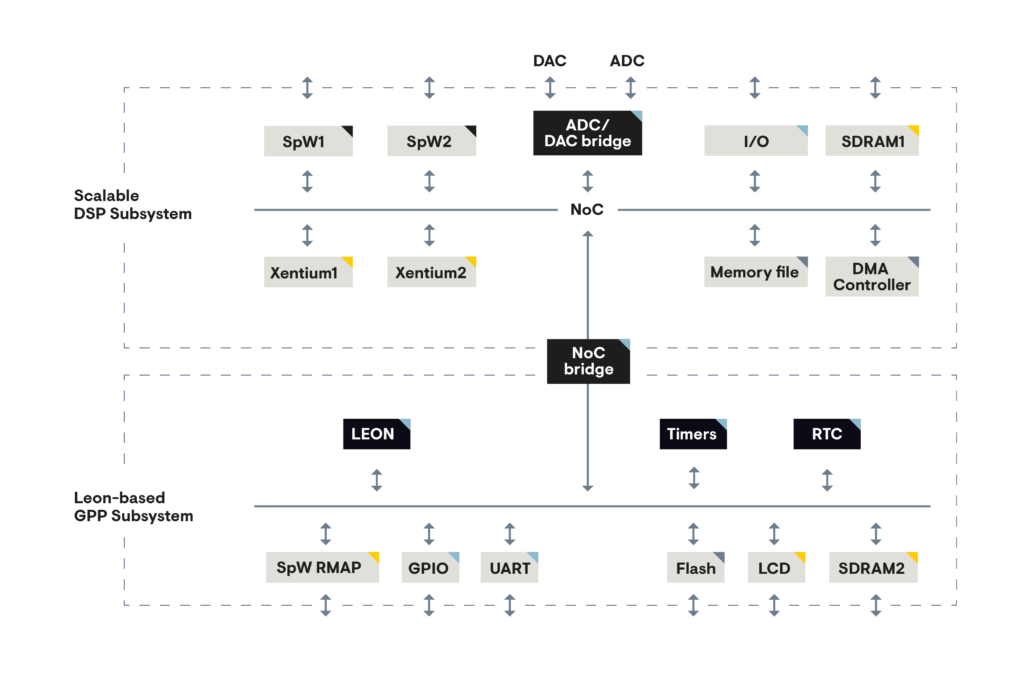

Wij hebben op basis van onze Xentium DSP IP een werkend prototype ontwikkeld van een betrouwbare dataprocessor voor signaalverwerking tijdens ruimtemissies (on-board payload processing). Het prototype werd geïmplementeerd met commerciële FPGA-technologie om de functionele aspecten van de multicore DSP SoC-architectuur te valideren.

Het prototype was bestand tegen datafouten, zowel op software- als hardwareniveau. De architectuur bestond uit een SoC met daarin geïntegreerd meerdere Xentium DSP-cores, SpaceWire-interfaces (met ondersteuning voor RMAP-protocols), CCSDS-timers, ADC/DAC-interfaces, een LEON-processor en on-chip en off-chip geheugens (met EDAC-bescherming) – alles in één enkel systeem.

In het algemeen worden data-interfaces direct verbonden met het Network-on-Chip van het Xentium DSP-subsysteem. Besturingsinterfaces en randapparaten worden geplaatst op de bus van het GPP-subsysteem (General Purpose Processor).

Stralingsbestendige ASIC

Als voorbereiding voor een betrouwbare dataprocessor voor ruimtemissies hebben wij de belangrijkste onderdelen van het werkende prototype-ontwerp stralingsbestendig gevalideerd in IMEC’s DARE 180nm CMOS-technologie.

Het prototype van de ASIC is geslaagd voor de functionele tests in een omgeving met volledige straling (SEL > 70 MeV/cm2/mg; SEE – SEU > 50 MeV/cm2/mg).

Scalable sensor data processor

De Xentium DSP-cores zijn goedgekeurd voor het voorlopige ontwerp van de schaalbare processor voor sensordata-verwerking (Scalable Sensor Data Processor). Het zijn verregaand geïntegreerde ‘mixed-signal’ dataprocessoren voor sensoren, instrumenten en verwerkings-units voor toekomstige wetenschappelijke en onderzoeksmissies. Ze bieden hoge prestaties, zijn schaalbaar en bestand tegen straling.

Achtergrondinformatie over SSDP vindt u hier:

Scalable sensor data processor: a multi-core payload data processor asic (pdf)

Scalable sensor data processor: development and validation (pdf)